There are two basic types: Register/Nets Register => For sequential logic most common type is “reg” the place where data is stored and hold their value before change. The method for dealing with the digital data in Verilog. Low performance, resource usage, power consumption slow, not for complex system, high power consumption, Large Space … Cost is low for manufacturing (no redundancies) If you want to sell, use ASIC, Application Specific Integrated Circuit, instead) 6/24 Development Efficiency One of the most popular HDL Less time, cost, error correcting for development For testing your Verilog code or need to change design very frequently. Two major languages: Verilog, VHDL (Very-high-speed integrated circuits HDL) Verilog: adv.

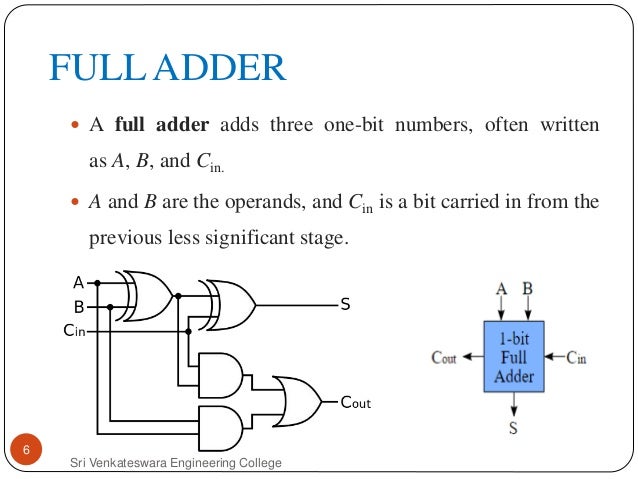

(-) Low performance, resource usage, power consumption slow, not for complex system, high power consumption, Large Space … Cost is low for manufacturing (no redundancies) If you want to sell, use ASIC, Application Specific Integrated Circuit, instead) 5/24Ħ Verilog Syntax Hardware Description Language (HDL)Īllows for modeling and simulation (with timing) of digital design Can be synthesized into hardware (netlist) by synthesis tools. Less time, cost, error correcting for development For testing your Verilog code or need to change design very frequently. Hardware Design Flow RTL Editor Simulation Logic Synthesis Gate Level Place & Route Post Gate Level Tape Out Designer RTL Code Gate Level Code Physical Layout Chip Verilog Level High Low Cost Basic Logic Design with Verilog, Kwon Suknam 3/24Ĥ Area Efficient FPGA Architecture For Datapath Circuits, Omesh MutukudaĪ field-programmable gate array (FPGA) an integrated circuit designed to be configured by a customer or a designer after manufacturing Field-Programmable Gate Array, Wikipedia Ref) Field-Programmable Gate Array, Wikipedia Area Efficient FPGA Architecture For Datapath Circuits, Omesh Mutukuda 4/24ĥ FPGA: Pros and Cons (+) Development Efficiency Introduction to Digital System and Microprocessor Design Inhwan Lee, Youngtaek Oh, Daehyun Ahn (inhwan301, koyt1126, 1/24Ģ Contents Hardware Design Flow FPGA Verilog: Half Adder Designģ Basic Logic Design with Verilog, Kwon Suknam Presentation on theme: "Week 5, Verilog & Full Adder"- Presentation transcript:

0 kommentar(er)

0 kommentar(er)